# DEC 3000 300/400/500/600/700 /800/900 AXP Models

# System Programmer's Manual

Order Number: EK-D3SYS-PM. B01

This manual describes the behavior of DEC 3000 AXP architecture as it pertains to writing system-level software, such as operating systems and drivers.

This manual describes the behavior of 300, 300L, 300X, 300LX, 400, 400S, 500, 500S, 500X, 600, 600S, 700, 800, 800S, and 900 models.

**Revision/Update Information:** This is a revised manual.

#### First Printing, September 1993 Revised, July 1994

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor.

© Digital Equipment Corporation 1994. All Rights Reserved.

The following are trademarks of Digital Equipment Corporation: Alpha AXP, AXP, Bookreader, DEC, DECaudio, DECchip, DECconnect, DEC GKS, DEC PHIGS, DECsound, DECwindows, DECwindows Motif, DECwindows Mail, DECwrite, DELNI, Digital, OpenVMS, OpenVMS AXP, RX26, ScriptPrinter, ThinWire, TURBOchannel, ULTRIX, VAX, VAX DOCUMENT, VAXcluster, VAXstation, and the Digital logo.

Other trademarks are as follows:

ISDN is a registered trademark of Fujitsu Network Switching of America.

All other trademarks and registered trademarks are the property of their respective holders.

**FCC Notice:** This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case users will be required to correct the interference at their own expense.

S2652

This document was prepared using VAX DOCUMENT Version 2.1.

## **Contents**

| Pr | eface .                                                     |                                                                                                                                                                                                                                                      | xiii                                                 |

|----|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1  | Introdu<br>AXP                                              | action to the DEC 3000 Models 300/400/500/600/700/800/900                                                                                                                                                                                            |                                                      |

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                      | System Description: 300 ModelsSystem Description: 400 ModelsSystem Description: 500 ModelsSystem Description: 600/700 ModelsSystem Description: 800/900 ModelsCPU Differences Among Models                                                           | 1–2<br>1–6<br>1–9<br>1–13<br>1–16<br>1–19            |

| 2  | Memor                                                       | y and I/O Addressing                                                                                                                                                                                                                                 |                                                      |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.5.1<br>2.5.2<br>2.6    | Memory Alignment<br>Memory Address Spaces<br>I/O Address Spaces<br>TURBOchannel Interface Bit Decode Map for I/O Addresses<br>CPU Registers<br>ABOX Control Register (ABOX_CTL)<br>Bus Interface Unit Control Register (BIU_CTL)<br>Bcache Tag Space | 2-2<br>2-3<br>2-7<br>2-9<br>2-9<br>2-11<br>2-12      |

| 3  | TURBO                                                       | Ochannel I/O Registers                                                                                                                                                                                                                               |                                                      |

|    | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3.1<br>3.2.3.2 | J 0 0 0                                                                                                                                                                                                                                              | 3–1<br>3–2<br>3–3<br>3–4<br>3–5<br>3–5<br>3–5<br>3–5 |

|    | 3.2.4<br>3.3<br>3.3.1                                       | Diagnostic LED Register (LED)—1.E000.0018<br>TURBOchannel Interface Registers (400/500/600/700/800/900 Models)<br>I/O Slot Configuration (IOSLOT) Register—1.C200.0000, 1.C200.0020                                                                  | 3–7<br>3–8                                           |

|    | 3.3.2                                                       | (Alternate address)                                                                                                                                                                                                                                  | 3–10                                                 |

|    | 3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8          | Register1.C200.0008Failing Address Register (FADR)1.C200.0010TURBOchannel Error Register (TCEREG)1.C200.0018Memory Configuration Registers1.Interrupt Mask Register (IMR)1.C240.0000Interrupt Register (IR)1.D480.0000Scatter/Gather Map1.           | 3–12<br>3–13<br>3–14<br>3–15<br>3–15<br>3–17<br>3–17 |

| 4 | Address ASIC Registers (400/500/600/700/800/900 Models)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1Memory Configuration Registers4-4.1.1Operation4-4.1.2Boot Time4-4.1.3Improper Configuration4-4.1.4Disabling Memory4-4.2Victim Address Register and Counter Register (VAR/VACR)4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 4.2.1Initialization4-4.2.2Writing the VACR4-4.2.3Reading the VAR4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 | Scatter/Gather (Virtual DMA) RAMs (400/500/600/700/800/900 Models)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.1Scatter/Gather Register Map5-5.2Organization5-5.3Writing and Reading Scatter/Gather Map Entries5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6 | CXTurbo Graphics Subsystem: 300/500 Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 6.1Comparison of Features6-6.2CXTurbo Address Map6-6.3Frame Buffer Control Registers6-6.4SFB ASIC Functions6-6.4.1Mode Register6-6.4.2Planemask Register6-6.4.3Raster Op Register6-6.4.4PixelMask Register6-6.4.5Foreground and Background Registers6-6.4.6PixelShift Register6-6.4.7Address Register6-6.4.8DEEP Register6-6.4.9START, BCONT, VIDEO_VALID, ENABLE_INTERRUPT,<br>CLEAR_INTERRUPT Registers6-6.4.10Video Timing Registers6-6.4.10.1Video Refresh Counter Register6-6.4.10.3Horizontal Setup Register6-6.4.10.4Vertical Timing Parameters Register6-6.4.11TCCLK COUNT, VIDCLK_COUNT Registers6-6.5Bt459 RAMDAC6-6.6System FEPROM (500 Models)6- |

| 7 | IOCTL ASIC and System Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 7.1       IOCTL Address Map       7-         7.2       System FEPROM       7-         7.3       IOCTL Registers Address Map       7-         7.3.1       LANCE DMA Pointer Register (LDP)—1.A004.0020/1.E004.0020       7-         7.3.2       Communication Port 1 Transmit DMA       7-         Pointer—1.A004.0030/1.E004.0030       7-                                                                                                                                                                                                                                                                                                                   |

TURBOchannel Reset Register (TCRESET)—1.C2A0.0000 ....

3–19

3.3.9

| 7.3.3  | Communication Port 1 Receive DMA                         |      |

|--------|----------------------------------------------------------|------|

|        | Pointer—1.A004.0040/1.E004.0040                          | 7–7  |

| 7.3.4  | Printer Port Transmit DMA Pointer—NA/ 1.E004.0050        | 7–8  |

| 7.3.5  | Printer Port Receive DMA Pointer—NA/1.E004.0060          | 7–8  |

| 7.3.6  | ISDN Transmit DMA Pointer—1.A004.0080/1.E004.0080        | 7–8  |

| 7.3.7  | ISDN Transmit DMA Buffer Pointer—1.A004.0090/1.E004.0090 | 7–8  |

| 7.3.8  | ISDN Receive DMA Pointer—1.A004.00A0/1.E004.00A0         | 7–9  |

| 7.3.9  | ISDN Receive DMA Buffer Pointer—1.A004.00B0/1.E004.00B0  | 7–9  |

| 7.3.10 | Data buffers                                             |      |

|        | 3-0—1.A004.00C0-1.A004.00F0/1.E004.00C0-1.E004.00F0      | 7–9  |

| 7.3.11 | System Support Register—1.A004.0100/1.E004.0100          | 7–10 |

| 7.3.12 | System Interrupt Register (SIR)—1.A004.0110/1.E004.0110  | 7–12 |

| 7.3.13 | System Interrupt Mask Register—1.A004.0120/1.E004.0120   | 7–15 |

| 7.3.14 | System Address Register—1.A004.0130/1.E004.0130          | 7–15 |

| 7.3.15 | ISDN Data Transmit Register—1.A004.0140/1.E004.0140      | 7–16 |

| 7.3.16 | ISDN Data Receive Register—1.A004.0150/1.E004.0150       | 7–16 |

| 7.3.17 | LANCE I/O Slot Register—1.A004.0160/1.E004.0160          | 7–16 |

| 7.3.18 | SCC-0 DMA Slot Register—1.A004.0180/1.E004.0180          | 7–17 |

| 7.3.19 | SCC-1 DMA Slot Register—1.A004.0190/1.E004.0190          | 7–17 |

| 7.4    | Ethernet Station Address ROM Addresses                   | 7–18 |

| 7.5    | LANCE Register Addresses                                 | 7–21 |

| 7.6    | SCC Register Addresses                                   | 7–21 |

| 7.7    | RTC Register Addresses                                   | 7–23 |

| 7.8    | ISDN Register Addresses                                  | 7–24 |

| 7.8.1  | ISDN Register Addresses (300 Models)                     | 7–24 |

| 7.8.2  | ISDN Register Addresses (400/500/600/700/800/900 Models) | 7–26 |

## 8 TURBOchannel Dual SCSI ASIC

| 8.1   | TURBOchannel Dual SCSI Address Map                          | 8–2  |

|-------|-------------------------------------------------------------|------|

| 8.2   | Internal Registers                                          | 8–3  |

| 8.2.1 | Control Interrupt Register (CIR)—1.8004.0000/1.C004.0000    | 8–4  |

| 8.2.2 | Interrupt Mask Enable Register                              |      |

|       | (IMER)—1.8004.0004/1.C004.0004                              | 8–7  |

| 8.2.3 | SCSI[x] DMA Address Register (SDAx)—1.8004.1x00/1.C004.1x00 | 8–8  |

| 8.2.4 | SCSI[x] DMA Interrupt Control Register                      |      |

|       | (DICx0)—1.8004.1x04/1.C004.1x04                             | 8–9  |

| 8.2.5 | SCSI[x] DMA Unaligned Data[0]                               |      |

|       | (DUDx0)—1.8004.1x08/1.C004.1x08                             | 8–10 |

| 8.2.6 | SCSI[x] DMA Unaligned Data[1]                               |      |

|       | (DUDx1)—1.8004.1x0C/1.C004.1x0C                             | 8–11 |

| 8.3   | NCR 53C94 Registers (300/400/500 Models)                    | 8–12 |

| 8.4   | NCR 53CF94-2 Registers (600/700/800/900 Models)             | 8–13 |

| 8.5   | DMA buffers                                                 | 8–14 |

## 9 I/O Programming

| 9.1   | I/O Read and Write Restrictions          | 9–2 |

|-------|------------------------------------------|-----|

| 9.2   | DMA                                      | 9–3 |

| 9.2.1 | Physical DMA                             | 9–3 |

| 9.2.2 |                                          | 9–3 |

|       | Interrupt Handling During I/O Operations | 9–4 |

| 9.4   | TURBOchannel Usage (System-Specific)     | 9–5 |

| 9.4.1 | DMA Size                                 | 9–5 |

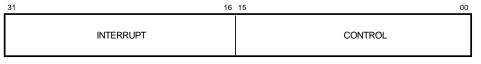

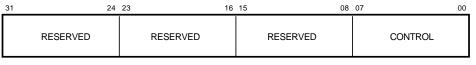

| 9.4.2    | DMA Arbitration                                              | 9–5  |

|----------|--------------------------------------------------------------|------|

| 9.4.2.1  | DMA Arbitration (300 Models)                                 | 9–5  |

| 9.4.2.2  | DMA Arbitration (400/500/600/700/800/900 Models)             | 9–6  |

| 9.4.3    | I/O Timeout                                                  | 9–6  |

| 9.4.4    | I/O Conflicts                                                | 9–7  |

| 9.4.5    | Masked I/O Read Operations                                   | 9–7  |

| 9.4.5.1  | 300 Models: Masked I/O Read Operations with a Non-Zero Byte  |      |

|          | Mask                                                         | 9–7  |

| 9.4.5.2  | 400/500/600/700/800/900 Models: I/O Read Operations with a   |      |

|          | Non-Zero Byte Mask                                           | 9–7  |

| 9.5 JU   | NKIO Subsystem                                               | 9–8  |

| 9.5.1    | IOCTL ASIC Overview                                          | 9–8  |

| 9.5.2    | I/O Programming and System FEPROM                            | 9–9  |

| 9.5.2.1  | Ethernet Station Address ROM                                 | 9–9  |

| 9.5.2.2  | LANCE Interface                                              | 9–9  |

| 9.5.2.3  | LANCE DMA                                                    | 9–10 |

| 9.5.2.4  | Serial Communications Controller (SCC)                       | 9–10 |

| 9.5.2.5  | DMA for Communication Transmit Port and Printer Port         | 9–11 |

| 9.5.2.6  | DMA for Communication Receive Port and Printer Port          | 9–12 |

| 9.5.2.7  | Real-Time Clock (RTC)                                        | 9–13 |

| 9.5.2.8  | 79C30A (ISDN/audio) Interface                                | 9–13 |

| 9.5.2.9  | ISDN DMA                                                     | 9–14 |

| 9.5.2.10 | Diagnostic LEDs (400/500/600/700/800/900 Models)             | 9–14 |

| 9.6 SC   | SI Interface                                                 | 9–15 |

| 9.6.1    | SCSI Interface: Differences Among Models                     | 9–15 |

| 9.6.2    | Dual SCSI ASIC Configuration                                 | 9–15 |

| 9.6.3    | NCR 53C94 Configuration and Programming (300/400/500 Models) | 9–16 |

| 9.6.4    | 53CF94-2 Configuration and Programming (600/700/800/900      |      |

|          | Models)                                                      | 9–16 |

| 9.6.5    | Initiation of DMA Transfers                                  | 9–18 |

| 9.6.5.1  | Unaligned DMA Write Operation                                | 9–19 |

| 9.6.5.2  | Interrupt Service                                            | 9–19 |

| 9.6.6    | Aborting Transactions                                        | 9–19 |

## 10 Hardware Exceptions and Interrupts

| 10.1   | Sources of Errors and Interrupts                     | 10–2  |

|--------|------------------------------------------------------|-------|

| 10.2   | Behavior of System Hardware Under Errors             | 10–4  |

| 10.3   | System Error/Interrupt Matrix                        | 10–5  |

| 10.4   | Dual SCSI Error/Interrupt Matrix                     | 10–12 |

| 10.5   | Error Insertion for Testing Purposes                 | 10–14 |

| 10.6   | Assignment of CPU Interrupt Pins                     | 10–15 |

| 10.7   | Error Handling and Recovery                          | 10–15 |

| 10.8   | PAL Recovery Algorithms for Selected Errors          | 10–16 |

| 10.8.1 | Bcache Tag Error on DMA Read/Write                   | 10–16 |

| 10.8.2 | Bcache Tag Parity Error on CPU Reference, LDxL, STxC | 10–17 |

## 11 CPU Power Up and Initialization

| 11.1   | Processor initialization | 11–1 |

|--------|--------------------------|------|

| 11.1.1 | Power-On Reset Sequence  | 11–2 |

| 11.1.2 | SROM Sequence            | 11–2 |

| 11.1.3 | SYSROM Sequence          | 11–2 |

| 11.2   | Bcache Initialization    | 11–3 |

## 12 Firmware: Overview

| 12.1 | Overview of Power-Up Initialization Code | 12–3 |

|------|------------------------------------------|------|

| 12.2 | Overview of the Console                  | 12–4 |

| 12.3 | Overview of Extended Self-Test/Utilities | 12–4 |

| 12.4 | Overview of PALcode                      | 12–4 |

| 12.5 | Overview of the MIPS Emulator            | 12–5 |

## 13 DEC 3000 AXP Firmware ROMs

| 13.1 | DEC 3000 AXP Firmware ROM Format | 13–1 |

|------|----------------------------------|------|

| 13.2 | System and I/O ROM Contents      | 13–1 |

| 13.3 | System ROM Format                | 13–3 |

## 14 Powerup Initialization and Firmware Entry

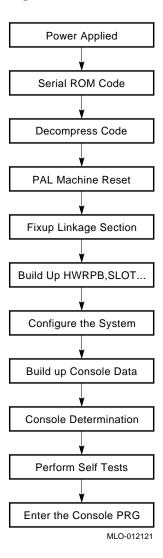

| 14.1   | Power-On Initialization Flow                    | 14–1  |

|--------|-------------------------------------------------|-------|

| 14.2   | Power-On Output                                 | 14–5  |

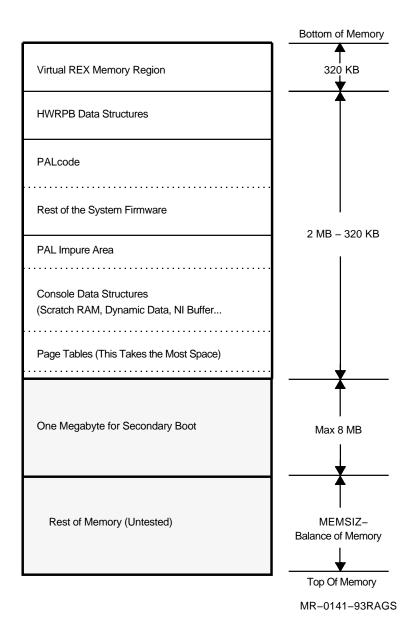

| 14.3   | Map of Memory Following Power-Up Initialization | 14–6  |

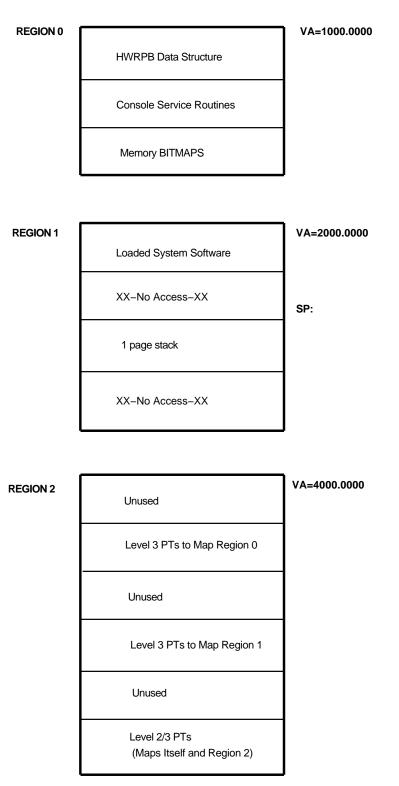

| 14.4   | Machine State Following Power-Up Initialization | 14–7  |

| 14.5   | System Firmware Entry                           | 14–9  |

| 14.5.1 | Restart                                         | 14–9  |

| 14.5.2 | Boot                                            | 14–9  |

| 14.5.3 | Halt                                            | 14–12 |

| 14.5.4 | Reentry Control                                 | 14–13 |

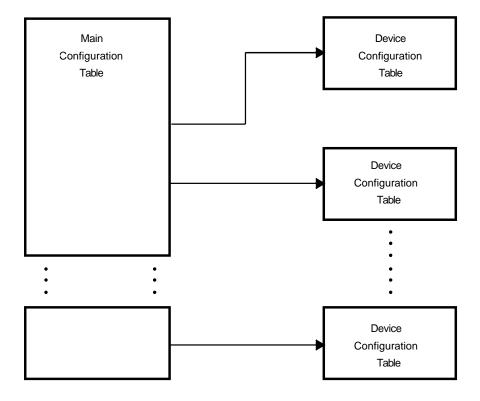

## 15 Configuration

| 15.1   | Main Configuration Table                   | 15–2 |

|--------|--------------------------------------------|------|

| 15.2   | Device Configuration Tables                | 15–3 |

| 15.2.1 | Kernel-Resident Device Configuration Table | 15–3 |

| 15.2.2 | TURBOchannel Device Configuration Table    | 15–6 |

## 16 Console

| 16.1   | Console Device                                      | 16–1 |

|--------|-----------------------------------------------------|------|

| 16.1.1 | Capabilities of Built-in Console Terminal: Keyboard | 16–2 |

| 16.1.2 | Capabilities of Built-in Console Terminal: Display  | 16–2 |

| 16.1.3 | Attached Terminals                                  | 16–3 |

| 16.1.4 | Built-In Terminals                                  | 16–3 |

| 16.2   | Console Saved State                                 | 16–4 |

| 16.3   | Console Program                                     | 16–4 |

| 16.3.1 | Entering and Exiting From Console Mode              | 16–4 |

| 16.3.2 | Console Operation                                   | 16–5 |

| 16.4   | Console Commands                                    | 16–7 |

| 16.4.1 | BOOT                                                | 16–7 |

| 16.4.2 | CONTINUE                                            | 16–9 |

| 16.4.3  | DEPOSIT                                     | 16–9  |

|---------|---------------------------------------------|-------|

| 16.4.4  | EXAMINE                                     | 16–14 |

| 16.4.5  | HALT                                        | 16–18 |

| 16.4.6  | HELP                                        | 16–18 |

| 16.4.7  | INITIALIZE                                  | 16–18 |

| 16.4.8  | LOGIN                                       | 16–19 |

| 16.4.9  | REPEAT                                      | 16–19 |

| 16.4.10 | SET[ENV]                                    | 16–20 |

| 16.4.11 | SHOW/PRINTENV                               | 16–25 |

| 16.4.12 | START                                       | 16–30 |

| 16.4.13 | TEST                                        | 16–30 |

| 16.4.14 | ! (COMMENT)                                 | 16–31 |

| 16.4.15 | Console Security                            | 16–31 |

| 16.4.16 | Console Password Register                   | 16–31 |

| 16.4.17 | Privileged Console Commands                 | 16–31 |

| 16.4.18 | Forgotten Password                          | 16–32 |

| 16.4.19 | 0 0                                         | 16–32 |

| 16.5    | Console Data Structures                     | 16–32 |

| 16.5.1  | HWRPB: General Information Portion          | 16–34 |

| 16.5.2  | HWRPB: Per-CPU Slot Portion                 | 16–38 |

| 16.5.3  | HWRPB: Console Terminal Block Portion       | 16–43 |

| 16.5.4  | HWRPB: Console Routine Block Portion        | 16–47 |

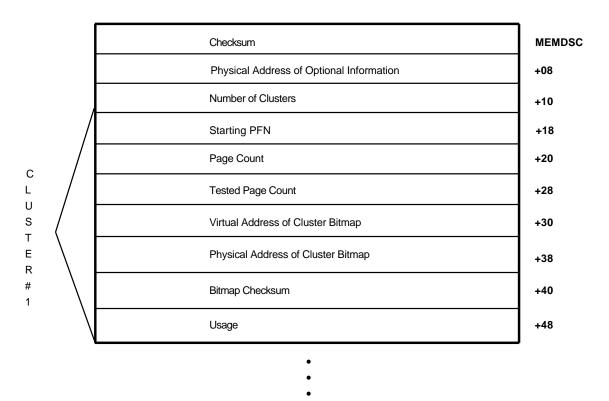

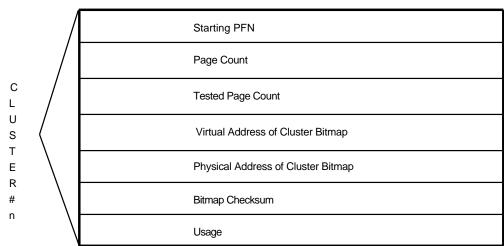

| 16.5.5  | HWRPB: Memory Data Descriptor Table Portion | 16–50 |

| 16.6    | Console Service Routine Overview            | 16–53 |

| 16.6.1  | The FIXUP Routine                           | 16–53 |

| 16.6.2  | The DISPATCH Routine                        | 16–54 |

| 16.7    | Console Service Routine Descriptions        | 16–54 |

|         | CLOSE                                       | 16–56 |

|         | FIXUP                                       | 16–57 |

|         | GETC                                        | 16–58 |

|         | GETENV                                      | 16–59 |

|         | IOCTL                                       | 16–60 |

|         | OPEN                                        | 16–62 |

|         | PROCESS_KEYCODE                             | 16–64 |

|         | PUTS                                        | 16–65 |

|         | READ                                        | 16–66 |

|         | RESETENV                                    | 16–68 |

|         | RESET_TERM                                  | 16–69 |

|         | SETENV                                      | 16–70 |

|         | SET_TERM_INTR                               | 16–72 |

|         | TERMCTL                                     | 16–73 |

|         | WRITE                                       | 16–74 |

|         |                                             |       |

## 17 DEC 3000 AXP PALcode

| 17.1 | Entering PALcode                | 17–1 |

|------|---------------------------------|------|

| 17.2 | Supported CALL_PAL Instructions | 17–2 |

| 17.3 | MACHINE_RESET PALcode           | 17–5 |

| 17.4 | Machine Check PALcode           | 17–5 |

| 17.5 | INTERRUPT PALcode               | 17–6 |

## 18 TURBOchannel Support

## 19 Nonvolatile RAM

| 19.1  | NVR Console Mailbox Register                   | 19–2  |

|-------|------------------------------------------------|-------|

| 19.2  | NVR Console Flags Register (CPFLG)             | 19–3  |

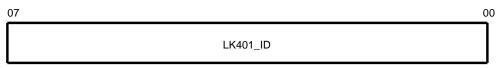

| 19.3  | NVR Keyboard Type Register                     | 19–4  |

| 19.4  | NVR Console Device Type Register               | 19–5  |

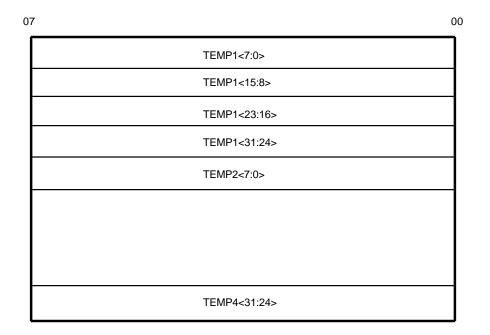

| 19.5  | Temporary Storage (TEMP)                       | 19–6  |

| 19.6  | NVR Battery Check Data (BAT_CHK)               | 19–6  |

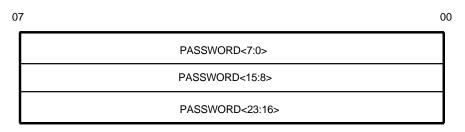

| 19.7  | Ethernet Trigger Password Code (PASSWORD)      | 19–7  |

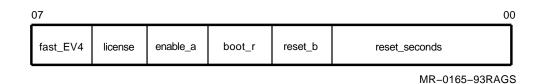

| 19.8  | NVR Security Flags                             | 19–7  |

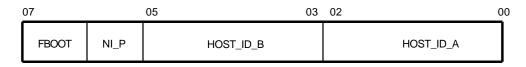

| 19.9  | NVR Default Boot Flags                         | 19–8  |

| 19.10 | NVR SCSI Information 1                         | 19–10 |

| 19.11 | NVR SCSI Information 2 (SCSI)                  | 19–10 |

| 19.12 | Default Boot Device Name Length (BOOT_DEV_LEN) | 19–11 |

| 19.13 | NVR Boot Device (BOOT_DEV)                     | 19–12 |

## A Dense and Sparse Space

| <b>4</b> —4<br><b>4</b> —4 |

|----------------------------|

| ∖–4                        |

|                            |

| 4–4                        |

| 4–5                        |

| 4–5                        |

| 6–۸                        |

| 4–7                        |

|                            |

## Glossary

## Index

## Examples

| Power-On Output Display     | 14–5                                                                                                                                                                                                                                                                                     |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Firmware Entry Code  | 14–10                                                                                                                                                                                                                                                                                    |

| Sample Boot Commands        | 16–9                                                                                                                                                                                                                                                                                     |

| Indirect Addressing         | 16–11                                                                                                                                                                                                                                                                                    |

| Sample Deposit Commands     | 16–13                                                                                                                                                                                                                                                                                    |

| Sample Examine Commands     | 16–16                                                                                                                                                                                                                                                                                    |

| Sample Halt Commands        | 16–18                                                                                                                                                                                                                                                                                    |

| Sample Help Command         | 16–19                                                                                                                                                                                                                                                                                    |

| Sample SET PASSWORD Command | 16–24                                                                                                                                                                                                                                                                                    |

| Sample SHOW CONFIG Command  | 16–26                                                                                                                                                                                                                                                                                    |

| Sample Show Device Command  | 16–26                                                                                                                                                                                                                                                                                    |

| Sample Show Error Command   | 16–27                                                                                                                                                                                                                                                                                    |

| Sample Show Memory Command  | 16–28                                                                                                                                                                                                                                                                                    |

| Test Command Examples       | 16–30                                                                                                                                                                                                                                                                                    |

|                             | System Firmware Entry CodeSample Boot CommandsIndirect AddressingSample Deposit CommandsSample Examine CommandsSample Halt CommandsSample Help CommandSample SET PASSWORD CommandSample SHOW CONFIG CommandSample Show Device CommandSample Show Error CommandSample Show Memory Command |

## Figures

| 1  | DEC 3000 AXP 300 Models: Functional Block Diagram          | 1–3   |

|----|------------------------------------------------------------|-------|

| 2  | DEC 3000 AXP 400 Models: Functional Block Diagram          | 1–6   |

| 3  | DEC 3000 AXP 500 Models: Functional Block Diagram          | 1–9   |

| 4  | DEC 3000 AXP 600/700 Models: Functional Block Diagram      | 1–13  |

| 5  | DEC 3000 AXP 800/900 Models: Functional Block Diagram      | 1–16  |

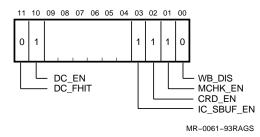

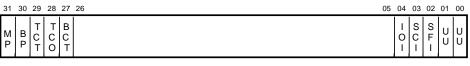

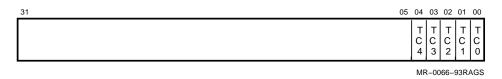

| 6  | ABOX_CTL Register: 300 Models                              | 2–9   |

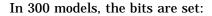

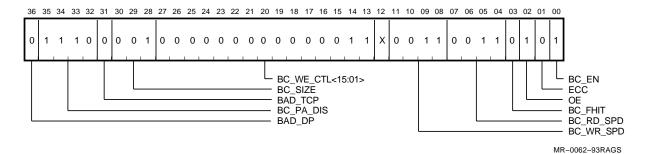

| 7  | ABOX_CTL Register: 400/500/600/700/800/900 Models          | 2–10  |

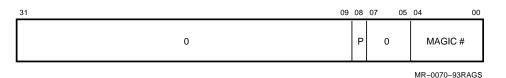

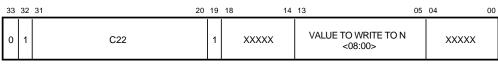

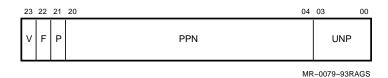

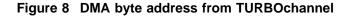

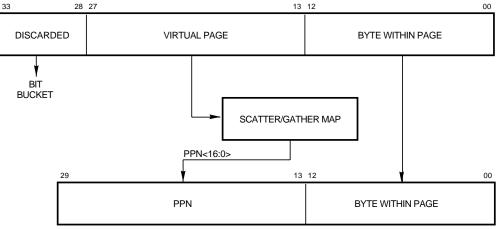

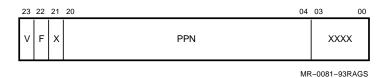

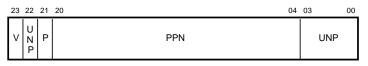

| 8  | DMA byte address from TURBOchannel                         | 5–2   |

| 9  | IOCTL Subsystem                                            | 7–1   |

| 10 | 400/500/600/700/800/900 Models: DMA Arbitration Scheme     | 9–6   |

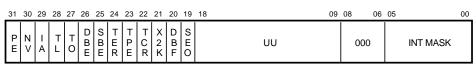

| 11 | Interrupt Stack Frame                                      | 10–5  |

| 12 | Corrected Error (Small) Logout Frame                       | 10–6  |

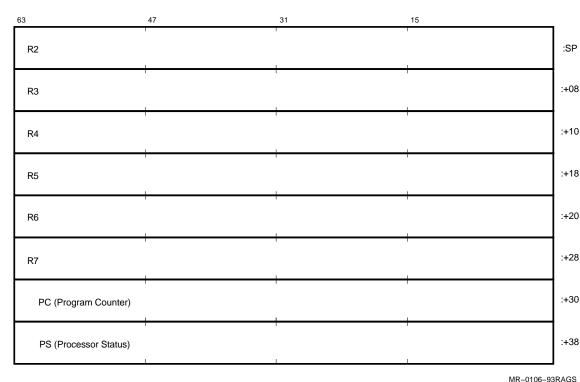

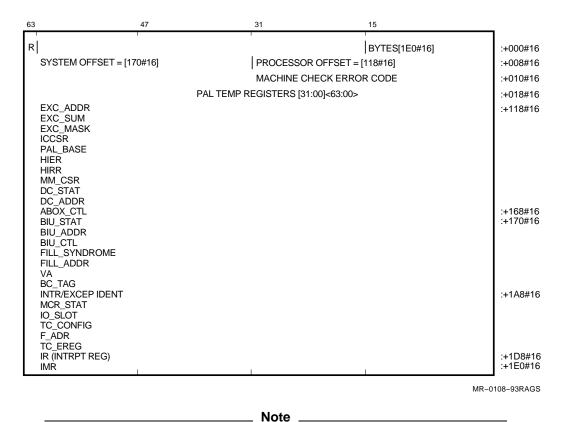

| 13 | Machine check (large) logout frame                         | 10–6  |

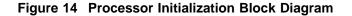

| 14 | Processor Initialization Block Diagram                     | 11–1  |

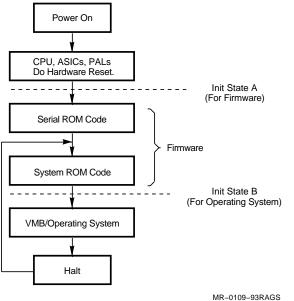

| 15 | System ROM Header Format                                   | 13–3  |

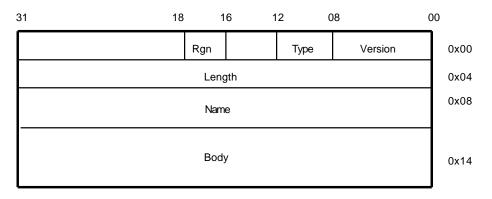

| 16 | Format of a ROM Object                                     | 13–5  |

| 17 | Power-On Initialization Flow                               | 14–2  |

| 18 | Map of Memory Following Power-Up Initialization            | 14–6  |

| 19 | Initial Boot Address Space                                 | 14–11 |

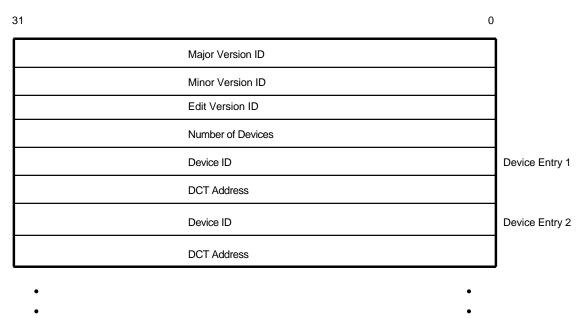

| 20 | Configuration Tables                                       | 15–1  |

| 21 | Main Configuration Table                                   | 15–2  |

| 22 | Kernel-Resident Device Configuration Table                 | 15–4  |

| 23 | TURBOchannel Device Configuration Table                    | 15–7  |

| 24 | Keyboard Menu Prompt                                       | 16–22 |

| 25 | General HWRPB Structure                                    | 16–33 |

| 26 | HWRPB General Information                                  | 16–35 |

| 27 | HWRPB Per-CPU Slot                                         | 16–39 |

| 28 | PALcode Revision Quadword                                  | 16–42 |

| 29 | Format of a Console Terminal Block (Decimal Values)        | 16–44 |

| 30 | Format of a Console Routine Block                          | 16–48 |

| 31 | Format of the Memory Data Descriptor Table                 | 16–51 |

| 32 | NVR Console Mailbox Register (CPMBX)                       | 19–2  |

| 33 | NVR Console Flags (CPFLG)                                  | 19–3  |

| 34 | NVR Keyboard Type Register (LK401_ID)                      | 19–4  |

| 35 | NVR Console Type Register (CONSOLE_ID)                     | 19–5  |

| 36 | NVR Temporary Storage (TEMP)                               | 19–6  |

| 37 | NVR Battery Check Data (BAT_CHK)                           | 19–6  |

| 38 | NVR Ethernet Trigger Password Code (PASSWORD)              | 19–7  |

| 39 | NVR Security Flags                                         | 19–7  |

| 40 | NVR Boot Flags                                             | 19–8  |

| 41 | NVR SCSI Information 1                                     | 19–10 |

| 42 | NVR SCSI Information 2                                     | 19–10 |

| 43 | NVR Default Boot Device Name Length (BOOT_DEV_LEN)         | 19–11 |

| 44 | NVR Default Boot Device (BOOT_DEV)                         | 19–12 |

| 45 | Dense I/O Space Addressing: 400/500/600/700/800/900 Models | A–2   |

|    |                                                            |       |

| 46 | Dense I/O Space Addressing: 300 Models                      | A–2 |

|----|-------------------------------------------------------------|-----|

| 47 | Sparse I/O Space Addressing: 400/500/600/700/800/900 Models | A–3 |

| 48 | Sparse I/O Space Addressing: 300 Models                     | A–3 |

## Tables

| 1  | Conventions Used in this Guide                                          | xv   |

|----|-------------------------------------------------------------------------|------|

| 2  | Bit Name Conventions Used in this Guide                                 | xvi  |

| 3  | System Jumpers                                                          | 1–5  |

| 4  | Memory Address Spaces                                                   | 2–2  |

| 5  | Memory Address Space Components                                         | 2–2  |

| 6  | 300 Model I/O Address Map                                               | 2–4  |

| 7  | 400/500/600/700/800/900 Models I/O Address Map                          | 2–5  |

| 8  | I/O Interface Registers (300 Models)                                    | 3–1  |

| 9  | TURBOchannel Control and Status Registers (300 Models)                  | 3–2  |

| 10 | TURBOchannel Control and Status Registers                               |      |

|    | (400/500/600/700/800/900) Models                                        | 3–8  |

| 11 | IMR—1.C281.FFFC                                                         | 3–16 |

| 12 | IR—1.D4C0.0000                                                          | 3–18 |

| 13 | Scatter/Gather Registers                                                | 5–1  |

| 14 | CXTurbo Address Map                                                     | 6–3  |

| 15 | Frame Buffer and Video Register Map                                     | 6–5  |

| 16 | IOCTL Address Map                                                       | 7–3  |

| 18 | System Address Register (300 Models)                                    | 7–15 |

| 19 | Ethernet Station Address ROM Addresses (400/500/600/700/800/900         |      |

|    | Models)                                                                 | 7–18 |

| 20 | Ethernet Station Address ROM Addresses (300 Models)                     | 7–19 |

| 21 | LANCE Register Addresses (400/500/600/700/800/900 Models)               | 7–21 |

| 22 | LANCE Register Addresses (300 Models)                                   | 7–21 |

| 23 | SCC Register Addresses (300 Models)                                     | 7–21 |

| 24 | SCC Register Addresses (400/500/600/700/800/900 Models)                 | 7–21 |

| 25 | RTC Register Addresses (300 Models)                                     | 7–23 |

| 26 | RTC Register Addresses (400/500/600/700/800/900 Models)                 | 7–23 |

| 27 | ISDN Direct Address Registers (300 Models)                              | 7–24 |

| 28 | ISDN Indirect Address Registers (300 Models)                            | 7–24 |

| 29 | ISDN Directly Addressed Registers (400/500/600/700/800/900              | 7 06 |

| 30 | Models)                                                                 | 7–26 |

| 30 | ISDN Indirectly Addressed Registers (400/500/600/700/800/900<br>Models) | 7–27 |

| 31 | TURBOchannel Dual SCSI Address Map                                      | 8–2  |

| 32 | TURBOchannel Dual SCSI ASIC Register Map                                | 8–3  |

| 33 | Baud Rate Programming                                                   | 9–11 |

| 34 | SCC Signal Connections                                                  | 9–12 |

| 35 | Dual SCSI Interface: Differences Among Models                           | 9–12 |

| 36 | Data Transfer Error Coverage                                            | 10–3 |

| 37 | Priority of PAL Entry Points                                            | 10-4 |

| 38 | System Error/Interrupt Matrix                                           | 10-4 |

| 50 | System Entri/Interrupt Matrix                                           | 10-1 |

| 39 | CPU State Before SCB Routines                         | 10–10 |

|----|-------------------------------------------------------|-------|

| 40 | Dual SCSI Error/Interrupt Matrix                      | 10–12 |

| 41 | Error Insertion Techniques                            | 10–14 |

| 42 | Interrupt Pin Allocation                              | 10–15 |

| 43 | Memory Differences                                    | 12–1  |

| 44 | TURBOchannel Differences                              | 12–2  |

| 45 | Diagnostic LED Displays and Locations                 | 12–2  |

| 46 | 300 Model SROM Power-On Sequence                      | 14–3  |

| 47 | 400/500/600/700/800/900 Model SROM Power-On Sequence  | 14–4  |

| 48 | Register Values After Power-Up                        | 14–7  |

| 49 | Processor Restart Codes                               | 14–13 |

| 50 | Kernel-Resident Device Configuration Table Components | 15–5  |

| 51 | TURBOchannel Device Configuration Table Components    | 15–8  |

| 52 | DEC 3000 AXP Device IDs                               | 15–8  |

| 53 | Console Saved State                                   | 16–4  |

| 54 | VMS and OSF Device Naming Conventions                 | 16–8  |

| 55 | Symbolic Addresses—General                            | 16–12 |

| 56 | Diagnostic Environment Values                         | 16–21 |

| 59 | POWERUP_TIME Settings                                 | 16–24 |

| 58 | Language Selection Codes                              | 16–28 |

| 59 | POWERUP_TIME Settings                                 | 16–29 |

| 60 | Service Routines accessed by the DISPATCH ROUTINE     | 16–54 |

| 61 | Console Service Routines                              | 16–54 |

| 62 | Environment Variable ID Numbers                       | 16–70 |

| 63 | PALcode Entry Points                                  | 17–2  |

| 64 | Supported CALL_PAL Instructions                       | 17–2  |

| 65 | TURBOchannel Option ROM Base Addresses                | 18–1  |

| 66 | NVR Storage Allocation                                | 19–1  |

| 67 | NVR Console Mailbox Register Fields                   | 19–2  |

| 68 | NVR Console Flags (CPFLG) Fields                      | 19–3  |

| 69 | NVR Language Selection Codes                          | 19–4  |

| 70 | NVR: Defined Console Devices                          | 19–5  |

| 71 | NVR Security Flags                                    | 19–7  |

| 72 | NVR SCSI Information 1 fields                         | 19–10 |

| 73 | NVR SCSI Information 2 Fields                         | 19–10 |

| 74 | Minimum Granularity                                   | A-4   |

| 75 | Effect of Load and Store Instructions in Dense Space  | A–5   |

| 76 | Effect of Load and Store Instructions in Sparse Space | A–5   |

| 77 | Writing 32-Byte Blocks to the TURBOchannel Interface  | A–6   |

| 78 | How to Address I/O Registers                          | A–7   |

## Preface

The DEC 3000 300/400/500/600/700/800/900 AXP Models are a family of highperformance deskside and desktop workstations that use Digital's DECchip 21064 RISC-style microprocessor. They comprise a family of systems based on the Digital Alpha AXP architecture, providing a 64-bit computing environment.

## **Intended Audience**

This manual is intended for design engineers and programmers who write such system-level software as operating systems and drivers. The manual discusses the format and behavior of specific hardware architecture as it pertains to writing system-level programs.

#### **Document Contents**

The *DEC 3000 300/400/500/600/700/800/900 AXP Models System Programmer's Manual* is divided into 19 chapters, one appendix, one glossary, and one index:

- Chapter 1 describes the system and the variations among models.

- Chapter 2 describes the DEC 3000 AXP systems' address maps, the methods of addressing I/O space, and system I/O registers, specifically: memory alignment, memory address spaces, I/O address space, the TURBOchannel interface bit decode map for I/O addresses, and address-processing and Bcache control CPU registers.

- Chapter 3 discusses I/O interface registers—the 300 models' I/O control and status registers and the 400/500/600/700/800/900 models' TURBOchannel control and status Registers.

- Chapter 4 discusses the 400/500/600/700/800/900 models' address ASIC, which controls access to each memory configuration register and to the victim address counter register and victim address register for caching.

- Chapter 5 discusses the scatter/gather maps used in 400/500/600/700/800/900 models to support virtual DMA—the location, size, and access modes of scatter/gather registers, their organization, and the performance of read and write operations on scatter/gather map entries.

- Chapter 6 discusses the CXTurbo graphics subsystem, and covers these topics: CXTurbo address map, I/O address map, Frame Buffer Control Register, SFB ASIC functions, Bt459 RAMDAC, and System FEPROM (400/500/600/700/800 /900 models).

- Chapter 7 discusses the IOCTL ASIC and system registers—the IOCTL address map, system FEPROM, and IOCTL registers.

- Chapter 8 discusses the TURBOchannel Dual SCSI ASIC—address map, internal registers, 53C94 registers, and DMA buffers.

- Chapter 9 describes programming considerations and restrictions for I/O transactions—I/O read and write restrictions, DMA, interrupt handling during I/O operations, TURBOchannel usage (system-specific), JUNKIO subsystem, and the dual SCSI interface.

- Chapter 10 discusses the behavior of the system under hardware exceptions and interrupts—sources of errors and interrupts, behavior of system hardware under errors, system error/interrupt matrix, dual SCSI error/interrupt matrix, error insertion for testing purposes, assignment of CPU interrupt pins, error handling and recovery, and PAL recovery algorithms for selected errors.

- Chapter 11 discusses processor and Bcache initialization.

- Chapter 12 gives an overview of DEC 3000 AXP firmware.

- Chapter 13 discusses DEC 3000 AXP firmware ROMs—firmware ROM format, system and I/O ROM contents, and system ROM format.

- Chapter 14 discusses firmware power-up initialization and entry—power-on initialization flow, map of memory following power-up initialization, machine state following power-up initialization, SROM routines, and system firmware entry.

- Chapter 15 discusses configuration information saved by power-up initialization code—the main configuration table and the device configuration tables.

- Chapter 16 discusses the console device, console saved state, console program, and console data structures, and gives an overview and descriptions of console service routines.

- Chapter 17 discusses DEC 3000 AXP PALcode—location, entering PALcode, supported CALL\_PAL instructions, MACHINE\_RESET PALcode, machine-check PALcode, and INTERRUPT PALcode.

- Chapter 18 discusses TURBOchannel support.

- Chapter 19 discusses nonvolatile RAM and its data structures.

- Appendix A discusses the use of dense and sparse space in I/O programming the layout of dense and sparse addressing locations, the required number of transactions to complete operations through dense and sparse space, minimum read and write granularity of operations through dense and sparse space, the effect of load and store instructions in dense and sparse space, byte-masked I/O read operations, and mapping I/O Addresses.

- A Glossarycontains useful terms and their meaning.

### **Associated Documents**

- Alpha Architecture Handbook (EC-H1689-10)

- Alpha Architecture Reference Manual (EY-L520E-DP)

- Bt459 RAMDAC Specification

- DECchip 21064 Microprocessor Chip Data Sheet (EC-F1720-10)

- DECchip 21064-AA Microprocessor Hardware Reference Manual (EC–N0079– 72)

- *DEC 3000 Model 300/300L/300X/300LX AXP Service Documentation Kit* (EK–PELSV–DK)

- DEC 3000 Model 400 AXP Workstation Documentation Kit (EK-SNDPR-DK)

- DEC 3000 Model 400/400S AXP Server Documentation Kit (EK-SNPSV-DK)

- DEC 3000 Model 500/500S AXP Server Documentation Kit (EK-FLAMI-DK)

- DEC 3000 Model 500/500S AXP Workstation Kit (EK-FLMNG-DK)

- DEC 3000 Model 500X AXP Documentation Kit (EK–D5AXP–DK)

- DEC 3000 Model 600/600S/700 AXP Information Kit (EK-SNDWS-DK)

- DEC 3000 Model 800/800S/900 AXP Information Kit (EK-FLMWS-DK)

- NCR 53C94-95-96 Advanced SCSI Controller (1992)

- NCR 53CF94/96-2 Fast SCSI Controller (1992)

- TURBOchannel Specification Revision C (EK-TCDEV-DK)

- AMD79C30A ISDN Chip Specification

#### Conventions

Table 1 lists the conventions used in this guide.

Table 1 Conventions Used in this Guide

| Convention         | Description                                                                                                                                                                    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <x:y></x:y>        | Represents a bit field or an extent of a set of lines or signals ranging from x through y. For example, R0<7:4> indicates bits 4 through 7 in the general purpose register R0. |

| xy                 | Represents a range of bits from x to y.                                                                                                                                        |

| n, n <sub>10</sub> | Numbers are hexadecimal unless otherwise marked with a subscript number. If there is possible ambiguity, the radix is explicitly stated.                                       |

| 1.FFFF.FFFF        | Nine digit numbers typically represent 34-bit hexadecimal addresses and are grouped in four-digit clusters, separated by periods.                                              |

| Note               | A note contains information that might be of special importance to the user.                                                                                                   |

| Caution            | A caution contains information that the user needs to know to avoid damaging the software or hardware.                                                                         |

| Italics            | Italics indicate variables in code.                                                                                                                                            |

| []                 | Represents a command parameter, option, or qualifier that is optional.                                                                                                         |

Note \_\_\_\_\_

Direct technical questions regarding these products or this manual to the Digital Customer Service support telephone line at 1-800-354-9000.

Table 2 lists the conventions for naming bits:

| Convention    | Description                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | Describes a bit that is ignored on write operations and is read as 0.                                                                                                                                          |

| 1             | Describes a bit that is ignored on write operations and is read as 1.                                                                                                                                          |

| R/W           | Read/write. A bit or field that may be read or written by software.                                                                                                                                            |

| RO            | A read-only bit that can be read by software. It is written<br>by hardware. Software writes are ignored.                                                                                                       |

| WO            | Write-only. A write-only bit that can be written by software. It is used by hardware. Reads by software return unpredictable results.                                                                          |

| W             | A write bit that can be written by software. It is used by hardware. Reads by software return a 0.                                                                                                             |

| WC            | Write-one-to-clear. Software writes of a 1 cause this bit<br>to be cleared by hardware. Software writes of a 0 do not<br>modify the state of the bit.                                                          |

| W0C           | Write-zero-to-clear. Software writes of a 0 cause this bit<br>to be cleared by hardware. Software writes of a 1 do not<br>modify the state of the bit.                                                         |

| WA            | Write-anything. Software writes of any value to the register cause the bit to be cleared by hardware.                                                                                                          |

| RC            | Read-to-clear. The value is written by hardware and<br>remains unchanged until read by software, at which point<br>hardware may write a new value into the field.                                              |

| IGN           | These bits or fields are ignored when written.                                                                                                                                                                 |

| RAZ           | Read-as-zero. These bits or field return a zero when read.                                                                                                                                                     |

| MBZ           | Must-be-zero. These bits or fields must never be written<br>by software with a non-zero value. A reserved operand<br>exception occurs if a non-zero value in a MBZ fields is<br>encountered by the processor.  |

| SBZ           | Should-be-zero. These bits or fields should be filled by<br>software with a zero vlue. These fields may be used at<br>a future time. Nonzero values in SBZ fields produce<br>unpredictable results.            |

| RES/Reserved  | Reserved. These bits or fields are reserved for future expansion.                                                                                                                                              |

| Х             | A don't-care bit. The value of a don't-care bit is ignored.                                                                                                                                                    |

| UNDEFINED     | Triggered by privileged software, this type of value may halt the processor or cause it to lose information.                                                                                                   |

| UNPREDICTABLE | Triggered by either privileged or unprivileged software,<br>this type of result or occurrence does not disrupt the basic<br>operation of the processor. Unpredictable results may<br>acquire arbitrary values. |

Table 2 Bit Name Conventions Used in this Guide

1

# Introduction to the DEC 3000 Models 300/400/500/600/700/800/900 AXP

The DEC 3000 Models 300/400/500/600/700/800/900 AXP is a family of desktop and deskside workstations that support the DECchip 21064–AA CPU implementation of the Alpha AXP architecture. These models' I/O system is TURBOchannel-based and has embedded I/O devices.

This chapter briefly describes the components and functions of each model and covers the following topics:

- System description: 300 models (Section 1.1)

- System description: 400 models (Section 1.2)

- System description: 500 models (Section 1.3)

- System description: 600 models (Section 1.4)

- System description: 700 models (Section 1.4)

- System description: 800 models (Section 1.5)

- System description: 900 models (Section 1.5)

- Differences among Models (Section 1.6)

## 1.1 System Description: 300 Models

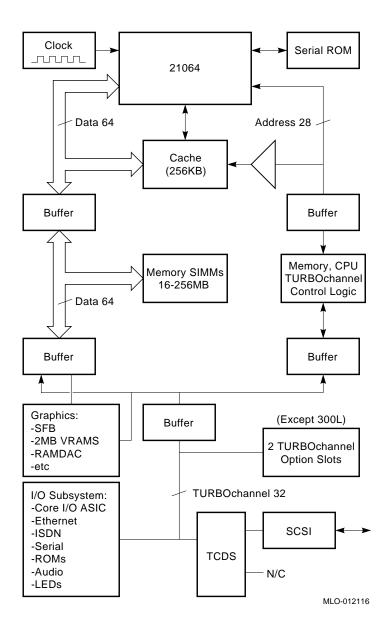

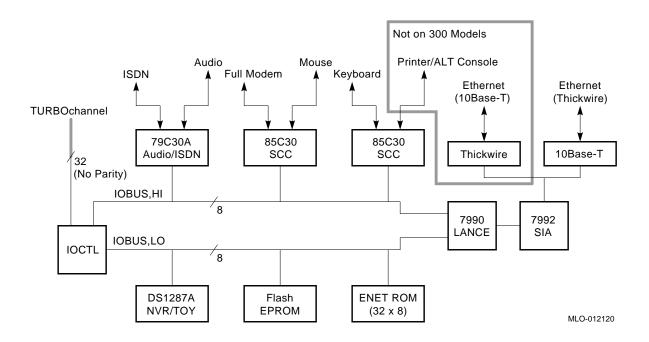

Figure 1 is a functional block diagram of the DEC 3000 AXP 300 models.

Numbers along communication lines indicate their bus width.

Major system components are:

#### • CPU:

A DECchip 21064–AA CPU, including on-chip 8 KB instruction and 8 KB data caches, and a 64 KB (8 KB) serial boot ROM. Section 2.5 discusses CPU registers that must be assigned specific values at startup.

Cache:

A module-level write-back backup cache, or Bcache. The Bcache contains 256 KB, 32-byte blocks.

The cache tags are parity-protected, with separate parity bits for the address and control sections. The control section has a dirty bit and a valid bit. The valid bit is always set since the Bcache is initialized on power up with all valid memory blocks. During system operation, the write-update protocol used during DMA to maintain cache coherency assures that the Bcache blocks must never be invalidated.

Section 2.6 describes Bcache tag space.

Section 10.1 describes the Bcache as a source of errors and interrupts. Section 11.2 describes Bcache initialization.

#### Memory Banks:

16 MB - 256 MB system memory, longword-parity protected, consisting of up to four memory banks, each one of which must be populated by two SIMMS of the same type. Using 1M x 4 DRAMs, the minimum memory size is 16 MB. Using 4M x 4 DRAMs, the maximum memory size is 256 MB. System memory is longword parity-protected.

Section 2.2 discusses memory and I/O addressing; Section 3.2.3 discusses the Memory Configuration Register (MCR).)

#### TURBOchannel Interface:

A 12.5 MHz TURBOchannel interface for I/O, which is controlled by a TURBOchannel ASIC. Section 3.2 discusses I/O Control and Status Registers. Section 9.4 discusses TURBOchannel I/O programming. 300 models do not support block-mode write operations.

#### Graphics Subsystem

An 8-plane (2D) color graphics subsystem, called the CXTurbo, which is connected to the TURBOchannel. The SFB (smart frame buffer) ASIC controls this subsystem, which supports an 8-plane color monitor in the resolution/refresh rate combinations of:

- 1024 x 768 @ 72 Hz (300L model)

- 1280 x 1024 @ 72 Hz (300, 300X, and 300LX models)

The CXTurbo is different from other TURBOchannel devices, in that it is operated at the full TURBOchannel speed of 25 MHz and is accessible only in dense I/O space. Appendix A discusses the use of dense and sparse I/O space in the DEC 3000 AXP.

Chapter 6 describes the CXTurbo graphics subsystem.

#### • TURBOchannel Option Slots:

The 300, 300X, and 300LX models contain two TURBOchannel option slots. Each slot has 64 MB of I/O address space.

The 300L model contains no option slots.

#### • I/O Subsystem:

An interface called the JUNKIO subsystem, which is connected to the TURBOchannel. The IOCTL ASIC implements this interface. Chapter 7 describes IOCTL ASIC control of the subsystem and Section 9.5 discusses programming the subsystem, which provides:

- A nonvolatile time-of-year clock based on the Dallas Semiconductor DS 1287A Real-Time Clock (RTC)

- Three serial lines, through two Zilog SCC (Z85C30) dual UARTS (universal asynchronous receiver/transmitters)—SCC0 and SCC1

- \* Asynchronous for keyboard—Port A of SCC1

- \* Asynchronous for mouse—Port A of SCC0

- \* CCITT V.24/V.28 19.2 KB/s asynchronous/synchronous 25-pin plug for communications—Port B of SCC0.

- An AMD 79C30A (Revision E) chip, providing both an ISDN-S interface and voice-quality audio with a usable bandwidth of approximately 100 Hz

3000 Hz

The following audio interfaces are supported:

- \* The loudspeaker outputs of the 79C30A are connected to a speaker located inside the system box.

- \* The differential *ear-out* and *mic-out* signals from 79C30A lead to an external MJ4 telephone jack located on the rear I/O panel of the system box. This jack supports connections to a telephone handset or an operator headset.

- Ethernet through the AMD local area network controller for Ethernet (LANCE) adapter. The external interface to the Ethernet is a 10BaseT twisted pair connector.

- A 32 K x 8 Ethernet address ROM.

- 768 KB of Flash memory used for system firmware composed of three 256 KB flash memory Devices. Control bits in the System Support Register of the IOCTL ASIC select the memory devices.

- Access to two 4-bit LED displays to display a 2-digit hexadecimal code for diagnostic purposes. (See

The Ethernet, ISDN, audio, printer, and communications ports have DMA support.

#### • SCSI Interface:

A TURBOchannel dual SCSI interface chip (TCDS) is connected to the TURBOchannel bus, but only one NCR53C94 SCSI controller chip interfaces to the TCDS ASIC and provides a single-ended, 8-bit, 5 MB/s SCSI port. This port drives one SCSI drop inside the system box and is also available outside the box for further expansion.

Chapter 8 discusses the TURBOchannel Dual SCSI ASIC.

#### **Hardware Jumpers**

Table 3 lists system jumpers, their possible position, and the correspoding function.

| Jumper | Position | Function<br>Flash ROM Write Disable          |  |

|--------|----------|----------------------------------------------|--|

| W1     | 1 to 2   |                                              |  |

| W1     | 2 to 3   | Flash ROM Write Enable                       |  |

| W2     | 1 to 2   | Graphics Monitor as Console                  |  |

| W2     | 2 to 3   | Serial Comm Port as Console                  |  |

| W2     | 3 to 4   | SROM Port as Mini-Console (Digital use only) |  |

| W3     | 1 to 2   | Secure console enabled                       |  |

| W3     | 2 to 3   | Secure console disabled                      |  |

Table 3 System Jumpers

## 1.2 System Description: 400 Models

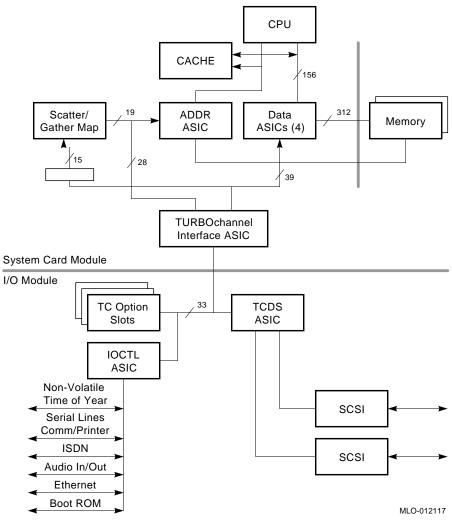

Figure 2 is a functional block diagram of the DEC 3000 AXP 400 models.

Figure 2 DEC 3000 AXP 400 Models: Functional Block Diagram

Numbers along communication lines indicate their bus width.

System components are:

• CPU:

A DECchip 21064–AA CPU, including on-chip 8-KB instruction and 8-KB data caches, and a 64-KB serial boot ROM. A 64-KB stream holds the primitive boot code for booting the operating system. Jumpers provide for the selection of up to seven other streams for diagnostic and other purposes. (The entire UVPROM is 64 K x 8.)

Section 2.5 discusses CPU registers that must be assigned specific values at startup.

• Cache:

A module-level write-back cache, or Bcache, consisting of 512 KB, 32-byte blocks, Single Bit Correction, Double Bit Detection (SBCDBD) ECC protected. The cache tags are parity-protected, with separate parity bits for the address and control sections. (There is only one bit of control, a dirty bit.)

Section 2.6 describes Bcache tag space.

Section 10.1 describes the Bcache as a source of errors and interrupts. Section 11.2 describes Bcache initialization.

#### • Scatter/Gather Map:

A 32K-entry scatter/gather map, for virtual DMA. Each entry maps an 8-KB Alpha AXP/DECchip 21064–AA page. Chapter 5 discusses the scatter/gather maps.

Address Path ASIC:

An address path ASIC.

#### • Datapath ASICs

Four datapath ASICs

#### • Memory Banks:

32 MB-512 MB system memory, SBCDBD ECC protected, consisting of up to two physical memory banks, each one of which must be populated by eight SIMMS of the same type. Using 1M x 4 DRAMs, the minimum memory size is 32 MB. Using 4M x 4 DRAMs, the maximum memory size is 512 MB.

Section 2.2 gives memory and I/O address spaces; Section 4.1 describes the format, operation, and proper configuration of Memory Configuration Registers.

#### • TURBOchannel Interface:

A 22.5 MHz TURBOchannel interface for I/O, which is controlled by a TURBOchannel ASIC. The interface has virtual DMA capability for any TURBOchannel option, high-speed block I/O write, and parity protection. Section 3.3 describes TURBOchannel Control and Status Registers. Section 9.4 discusses TURBOchannel I/O programming.

#### • TURBOchannel Option Slots:

Three TURBOchannel option slots. Each slot has 128 MB of I/O address space.

#### • JUNKIO Interface:

An interface called the JUNKIO subsystem, which is connected to the TURBOchannel. The IOCTL ASIC implements this interface. Chapter 7 describes IOCTL ASIC control of the subsystem and Section 9.5 discusses programming the subsystem, which provides:

- A nonvolatile time-of-year clock based on the Dallas Semiconductor DS 1287A Real-Time Clock (RTC)

- Four serial lines, through two Zilog SCC (Z85C30) dual UARTS (universal asynchronous receiver/transmitters)—SCC0 and SCC1.

- \* Asynchronous for keyboard

- \* Asynchronous for mouse

- \* Asynchronous for the printer, through 6-pin MMJ

- \* CCITT V.24/V.28 19.2 KB/s asynchronous/synchronous 25-pin plug for communications

- An ISDN-S interface, through an AMD 79C30A (Revision E) chip.

- Voice-quality audio I/O through the same AMD 79C30A (Revision E) chip, with a usable bandwidth of approximately 100-3000 Hz.

The audio lines extend from a connector located on the rear of the enclosure.

- Ethernet through an AMD local area network controller for Ethernet (LANCE) adapter. Both AUI transceiver (thickwire) and 10Base-T (twisted-pair) interfaces to Ethernet are provided. A setting in the system support register of IOCTL ASIC selects the interface.

- A 32 byte Ethernet address ROM.

- Two 256 KB writable console boot ROMs on the I/O module.

- Access to eight LEDs, used to display a hexadecimal code for diagnostic purposes.

The Ethernet, ISDN, audio, printer, and communications ports have DMA support.

#### SCSI Interface:

A dual SCSI interface chip (TCDS), which is connected to the TURBOchannel. Two NCR53C94 SCSI controller chips that interface to the TCDS ASIC provide two 5 MB/s 8-bit single-ended SCSI buses, with DMA support. Chapter 8 discusses the TURBOchannel Dual SCSI ASIC.

## 1.3 System Description: 500 Models

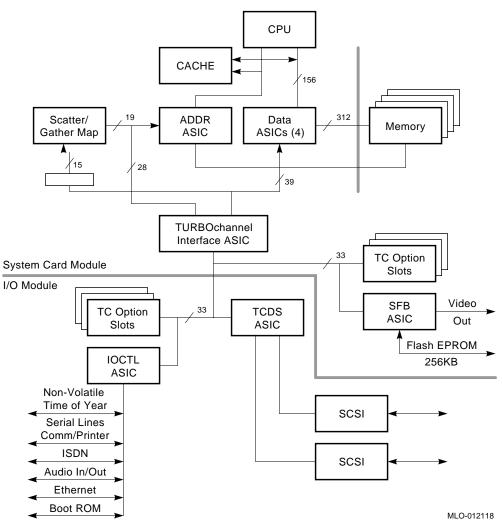

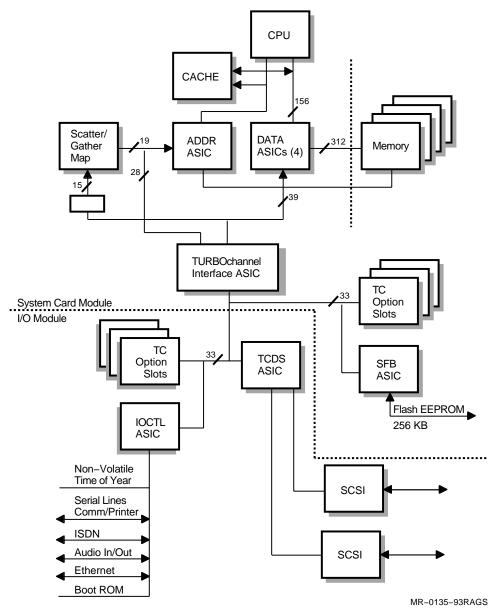

Figure 3 is a functional block diagram of the DEC 3000 AXP 500 models.

Figure 3 DEC 3000 AXP 500 Models: Functional Block Diagram

Numbers along communication lines indicate their bus width.

System components are:

• CPU:

A DECchip 21064–AA CPU, including on-chip 8-KB instruction and 8-KB data caches, and a 64-KB serial boot ROM. A 64-KB stream holds the primitive boot code for booting the operating system. Jumpers provide for the selection of up to seven other streams for diagnostic and other purposes. (The entire UVPROM is 64 K x 8.)

Section 2.5 discusses CPU registers must be assigned specific values at startup.

• Cache:

A module-level write-back cache, or Bcache, consisting of 512 KB, 32-byte blocks, Single Bit Correction, Double Bit Detection (SBCDBD) ECC protected. The cache tags are parity-protected, with separate parity bits for the address and control sections. (There is only one bit of control, a dirty bit.)

Section 2.6 describes Bcache tag space.

Section 10.1 describes the Bcache as a source of errors and interrupts. Section 11.2 describes Bcache initialization.

#### • Scatter/Gather Map:

A 32K-entry scatter/gather map, for virtual DMA. Each entry maps an 8 KB Alpha AXP/DECchip 21064–AA page. Chapter 5 discusses the scatter/gather maps.

#### Address Path ASIC:

An address path ASIC

Datapath ASICs

Four datapath ASICs

Memory Banks:

32 MB-1 GB system memory, SBCDBD ECC protected, consisting of up to four physical memory banks, each one of which must be populated by eight SIMMS. Using 1M x 4 DRAMs, the minimum memory size is 32 MB. Using 4M x 4 DRAMs, the maximum memory size is 1 GB.

Section 2.2 gives memory and I/O address spaces; Section 4.1 describes the format, operation, and proper configuration of Memory Configuration Registers.

#### • TURBOchannel Interface:

A 25 MHz TURBOchannel interface for I/O, which is controlled by a TURBOchannel ASIC. The interface has virtual DMA capability for any TURBOchannel option, high-speed block I/O write, and parity protection. Section 3.3 describes TURBOchannel Control and Status Registers. Section 9.4 discusses TURBOchannel I/O programming.

#### TURBOchannel Option Slots:

Six TURBOchannel option slots. Each slot has 128 MB of I/O address space.

#### • JUNKIO Interface:

An interface called the JUNKIO subsystem, which is connected to the TURBOchannel. The IOCTL ASIC implements this interface. Chapter 7 describes IOCTL ASIC control of the subsystem and Section 9.5 discusses programming the subsystem, which provides:

- A nonvolatile time-of-year clock based on the Dallas Semiconductor DS 1287A Real-Time Clock (RTC)

- Four serial lines, through two Zilog SCC (Z85C30) dual UARTS (universal asynchronous receiver/transmitters)—SCC0 and SCC1

- \* Asynchronous for keyboard

- \* Asynchronous for mouse

- \* Asynchronous for the printer, via 6-pin MMJ

- \* CCITT V.24/V.28 19.2 KB/s asynchronous/synchronous 25-pin plug for communications

- An ISDN-S interface, via an AMD 79C30A (Revision E) chip.

- Voice-quality audio I/O via the same AMD 79C30A (Revision E) chip, with a usable bandwidth of approximately 100-3000 Hz.

The audio connections provided are:

| Jack                                            | Function                                                                                                                                      |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| MJ<br>connector                                 | Telephone manager and companies devices                                                                                                       |  |

| 1/8" stereo<br>jack                             | Power speakers, stereo headsets (mono headsets require a stereo-<br>to-mono adapter jack, which is a stereo jack wired for mono<br>operation) |  |

| 1/8" mono<br>jack                               | Microphone in                                                                                                                                 |  |

| RCA jack Line In jack for external device input |                                                                                                                                               |  |

- Ethernet through an AMD local area network controller for Ethernet (LANCE) adapter. Both AUI transceiver (thickwire) and 10Base-T (twisted-pair) interfaces to Ethernet are provided. A setting in the system support register of IOCTL ASIC selects the interface.

- A 32 byte Ethernet address ROM.

- 256 KB of writable console ROM.

- Access to two 7-segment LEDs, used to display a 2-digit hexadecimal code for diagnostic purposes.

The Ethernet, ISDN, audio, printer, and communications ports have DMA support.

#### • Graphics Subsystem

An 8-plane color graphics subsystem, called the CXTurbo, which is connected to the TURBOchannel. The CXTurbo has 256 KB of writable console ROM and supports an 8-plane color monitor in the resolution/refresh rate combinations of:

- \* 1280 x 1024 @ 72 Hz

- \* 1280 x 1024 @ 66 Hz

The refresh rate is switch-selectable.

Chapter 6 describes the CXTurbo graphics subsystem.

#### • SCSI Interface:

A dual SCSI interface chip (TCDS), which is connected to the TURBOchannel. Two NCR53C94 SCSI controller chips that interface to the TCDS ASIC provide two 5 MB/s 8-bit single-ended SCSI buses, with DMA support.

Chapter 8 discusses the TURBOchannel Dual SCSI ASIC.

## 1.4 System Description: 600/700 Models

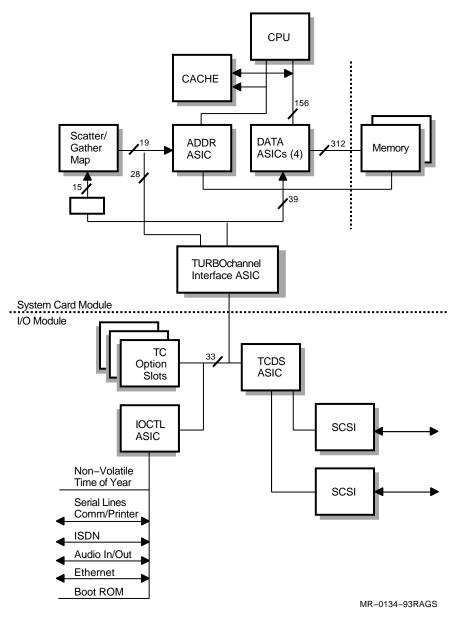

Figure 4 is a functional block diagram of the DEC 3000 AXP 600/700 models.

Numbers along communication lines indicate their bus width.

System components are:

• CPU:

A DECchip 21064–AA CPU, including on-chip 8-KB instruction and 8-KB data caches, and a 64-KB serial boot ROM. A 64-KB stream holds the primitive boot code for booting the operating system. Jumpers provide for the selection of up to seven other streams for diagnostic and other purposes. (The entire UVPROM is 64 K x 8.)

Section 2.5 discusses CPU registers that must be assigned specific values at startup.

• Cache:

A module-level write-back cache, or Bcache, consisting of 2 MB, 32-byte blocks, Single Bit Correction, Double Bit Detection (SBCDBD) ECC protected. The cache tags are parity-protected, with separate parity bits for the address and control sections. (There is only one bit of control, a dirty bit.)

Section 2.6 describes Bcache tag space.

Section 10.1 describes the Bcache as a source of errors and interrupts. Section 11.2 describes Bcache initialization.

#### • Scatter/Gather Map:

A 32K-entry scatter/gather map, for virtual DMA. Each entry maps an 8-KB Alpha AXP/DECchip 21064–AA page. Chapter 5 discusses the scatter/gather maps.

#### Address Path ASIC:

An address path ASIC

Datapath ASICs

Four datapath ASICs

Memory Banks:

32 MB-512 MB system memory, SBCDBD ECC protected, consisting of up to two physical memory banks, each one of which must be populated by eight SIMMS. Using 1M x 4 DRAMs, the minimum memory size is 32 MB. Using 4M x 4 DRAMs, the maximum memory size is 512 MB.

Section 2.2 gives memory and I/O address spaces; Section 4.1 describes the format, operation, and proper configuration of Memory Configuration Registers.

#### • TURBOchannel Interface:

A 25 MHz TURBOchannel interface for I/O, which is controlled by a TURBOchannel ASIC. The interface has virtual DMA capability for any TURBOchannel option, high-speed block I/O write, and parity protection. Section 3.3 describes TURBOchannel Control and Status Registers. Section 9.4 discusses TURBOchannel I/O programming.

#### TURBOchannel Option Slots:

Three TURBOchannel option slots. Each slot has 128 MB of I/O address space.

#### • JUNKIO Interface:

An interface called the JUNKIO subsystem, which is connected to the TURBOchannel. The IOCTL ASIC implements this interface. Chapter 7 describes IOCTL ASIC control of the subsystem and Section 9.5 discusses programming the subsystem, which provides:

- A nonvolatile time-of-year clock based on the Dallas Semiconductor DS 1287A Real-Time Clock (RTC)

- Four serial lines, through two Zilog SCC (Z85C30) dual UARTS (universal asynchronous receiver/transmitters)—SCC0 and SCC1

- \* Asynchronous for keyboard

- \* Asynchronous for mouse

- \* Asynchronous for the printer, through 6-pin MMJ

- \* CCITT V.24/V.28 19.2 KB/s asynchronous/synchronous 25-pin plug for communications

- An ISDN-S interface, through an AMD 79C30A (Revision E) chip.

- Voice-quality audio I/O through the same AMD 79C30A (Revision E) chip, with a usable bandwidth of approximately 100-3000 Hz.

The audio lines extend from a connector located on the rear of the enclosure.

- Access to eight LEDs, used to display a hexadecimal code for diagnostic purposes.

- Ethernet through an AMD local area network controller for Ethernet (LANCE) adapter. Both AUI transceiver (thickwire) and 10Base-T (twisted-pair) interfaces to Ethernet are provided. A setting in the system support register of IOCTL ASIC selects the interface.

- A 32 byte Ethernet address ROM.

- 512 KB of writable console ROM.

The Ethernet, ISDN, audio, printer, and communications ports have DMA support.